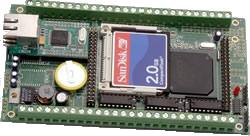

A C/C++ programmable controller based on the 32-bit 133 MHz AMD Elan SC520. It combines this high performance 5×86 generation processor with an extensive set of industrial I/O features on a single-board. The SC520 integrates an Am586 CPU and a high performance ANSI/IEEE 754 compliant hardware floating point unit (FPU). The SC520 has a total of seven timers including PIT timers and GP timers, plus a software timer.

A real-time clock (RTC) provides a time-of-day calendar and 114 bytes of battery backed RAM. 13 user programmable multifunctional I/O lines are available. One synchronous serial interface (SSI) supports full-duplex, high speed bi-directional communication. The SC520 supports 32 programmable multifunctional I/O lines (PIO) that can be used as general discrete I/O. The processor includes two industrial standard 16550-compatible UARTs, supporting baud rates up to 1.152 M baud. Both are RS232 by default, and one of the two can be modified with RS485 drivers.

Two additional UARTs can be optionally added; one availabe iwith RS232 or RS485 drivers, and the second with RS232 only. One synchronous serial interface (SSI) supports full-duplex, high speed bi-directional communication. By default, 256KW low power 55 ns SRAM is installed to allow longer battery backup lifetime; this requires slower 2 wait state access to memory.

Optionally, if battery backup is not required, a higher speed 20 ns SRAM can be installed to allow higher performance zero wait state operation. In additional to the on-board surface mount Flash, a 32-pin DIP IC socket allows using traditional user application plug-in ROM/Flash. A 50-pin CompactFlash interface supports low cost, removable, up to 2 GB mass storage CompactFlash cards with Windows compatible FAT file system support.

The 5D can be powered by a single unregulated DC power from 8V to 30V range with the on-board high-efficiency 5V switching regulator.

Networking/Connectivity

An Fast Ethernet Module can be installed to provide 100M BaseT network connectivity. The hardware LSI TCP/IP stack implements TCP/IP, UDP, ICMP and ARP in hardware. With 16KB internal transmit and receiving buffer, the Ethernet module releases internet connectivity and protocol processing from the host processor. The system can easily handle TCP/IP traffic of up to 200 Kbyte/s. Samples for HTTP, Telnet, FTP applications are available.

Industrial I/O

Industrial I/O

By default, 7 high voltage inputs(30V), and 14 high voltage sinking drivers(ULN2003A) are installed in DIP sockets with screw terminals. Each driver is capable of sinking 350 mA at 50V per line. They can directly drive solenoids, relays, or lights. Optionally, 12 DAC channels can be installed in their place. Four high isolation voltage photo couplers (PS2701, NEC) can be installed to provide optically isolation inputs. 16 additional input channels are provided with a 24-bit ADC(LTC2448), connected via screw terminal blocks. Voltage dividers are installed, allowing a default input range of 0-30V. They can be processed as flexible inputs for digital signals as well. With a peak sample rate of 5 KHz, this ADC works well directly with analog signals from strain gages, current shunts, RTDs, resistive sensors, and also work well directly with thermocouples in the differential mode. A precision reference(LT1019/REF02) with a internal temperature sensor providing local temperature for thermocouple applications.

Other Features

Signal lines on headers are 3.3V output and 5V input tolerant. Absolutely no voltage greater than 5V should be applied to any pins. With the 388 pin BGA package for the SC520, repair support is not available. The 5P can be powered by a single unregulated DC power from 8V to 30V range with the on-board high-efficiency 5V switching regulator (LM2575). The 5P can also be powered by a regulated 5V without using on-board 5V regulator.

The 5D shares a similar pin-out and physical dimensions with the R-Engine, i386-Engine, A-Engine, and a number of other similar ‘Engine’ boards. As compared to these other engine-based controllers, the 5D offers substantially more computing power at greater per-unit costs and power requirements. The 586-Engine-P is a similar unit, smaller in size and more suited for strictly data acquisition applications.

The 388 pin BGA package of the SC520 CPU makes repair support for the 586-Drive not available. A unique 16-bit parallel ADC (AD7655, 0-5V) supports ultra high-speed (1 MHz conversion rate) analog signal acquisition. The AD7655 contains two low noise, high bandwidth track-and-hold amplifiers that allow simultaneous sampling on two channels. Each track-and hold amplifier has a multiplexer in front to provide a total of 4 channels analog inputs.

The parallel ADC achieves very high throughput by requiring only two CPU I/O operations (one start, one read) to complete a 16-bit ADC reading. With a precision external 2.5V reference, the ADC accepts 0-5V analog inputs at 16- bit resolution of 0-65,535. (An optional +/-5V version based on the AD7665 may be available; contact us for details.) An octal rail-to-rail digital to analog converter (TLC2600) can be installed to provide eight channels of analog voltage (0-5V) outputs. At power on, all analog outputs are zero with the on-board reset.

The DAC chip is accessed through a 3-wire SPI-compatible serial interface, which is connected to the 5P high-speed synchronous serial port (clockable up to 50 MHz). Eight build-in analog output buffers can drive rail-to-rail analog voltage with up to 15 mA.

- 151x82mm DIN-rail mounting

- 32-bit CPU (AMD SC520), x86 compatible

- 133 MHz system clock

- High performance hardware floating point coprocessor

- Power consumption: 110 mA at 24V

- Up to 512 KB Flash/EPROM

- Up to 512 KB battery-backed non-volatile SRAM

- Four RS232/485 UARTs, 1 synchronous serial port

- 7 timers, 15 interrupts

- 16 analog or digital inputs (up to 30V) with 24-bit ADC

- 4 ch. 16-bit high-speed ADC

- 24 solenoid drivers, 4 opto-couplers, 10+ digital I/Os

- CompactFlash cards and FAT16 file system support

- Hardware high-performance TCP/IP stack on 100-T Ethernet

- Includes 133 MHz SC520 with 32 I/Os

- 1 synch. & 2 RS232

- 3 timers, RTC, watchdog timer

- 256 KW (16-bit) Flash

- 64 KW (16-bit) SRAM, battery + RTC

- switching regulators.

- Does not include add-on options

- OEM option discounts available.

EV-P/DV-P Kit $379/$829 (Software & 5D)

| Quantity | Price |

|---|---|

| 1 | CALL |

| 50 | CALL |

| 100 | CALL |

| 1,000+ | CALL |

Add-on Options:

| No. | Options | Price |

|---|---|---|

| 1 | SRAM: 256KW 55ns/20ns | $20/ $40 |

| 2 | CompactFlash Interface | $20 |

| 3 | 4 ch. 16-bit ADC (AD7655) 1 MHz | $40 |

| 4 | 8 ch. 16-bit DAC (LTC2600) | $40 |

| 5 | 100M BaseT Ethernet | $30 |

| 6 | SCC2691: a) RS232 (up to 2) b) RS485) | $30 x 2 |

| 7 | 16 channel 24-bit ADC (LT2448 0-30V) | $50 |

| 8 | OPTO couplers (PS2701) up to 4 | $10×4 |

| 9 | 2 ch. 12-bit DAC7612 (replacing HV outputs) | $20×3 |

| 10 | 192×128 graphic LCD | $50 |

| 11 | RS485 driver for SER1 | $10 |

Related Products